适用于高电流高功率应用的具有平面矩阵变压器的 LLC 转换器

近年来,在云计算和大数据的推动下,数据中心的兴起导致电力消耗大幅增加。仅在美国,到2014年,其用电量就超过700亿千瓦时,占全国总用电量的1.8%。

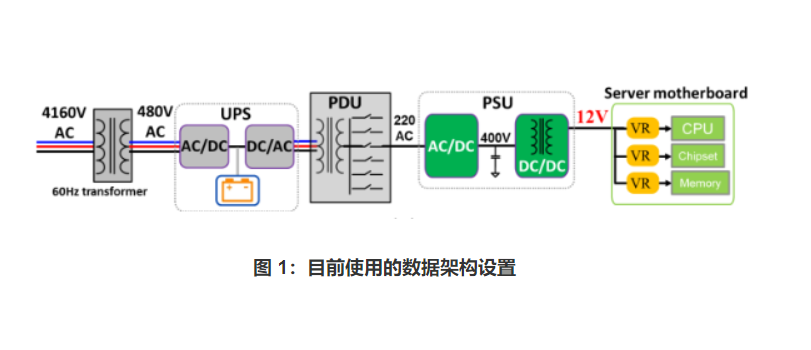

由于这种快速增长,满足不断增长的能源需求的需求不断增长,促使谷歌、Facebook、思科和 IBM 等行业领导者探索数据中心及其电源架构的创新替代方案。图 1 描述了使用 12V 总线的当前架构。

如上所述,依赖 12V 总线的传统设计会遭受过多的 i2R 损耗和多个能量转换级的影响,从而导致系统效率下降。为了解决这些低效率问题,正在向更高电压的配电总线(特别是 48V 和 400V)转变,国际电子制造倡议 (iNEMI) DC/DC 转换器标准化项目等举措就是例证。

然而,需要改进转换器技术,特别是 LLC 谐振转换器,以实现更高的效率和功率密度。这些转换器利用宽带隙器件和磁性结构等现代材料来增强性能,为未来的数据中心电源系统铺平道路。

平面矩阵变压器的集成

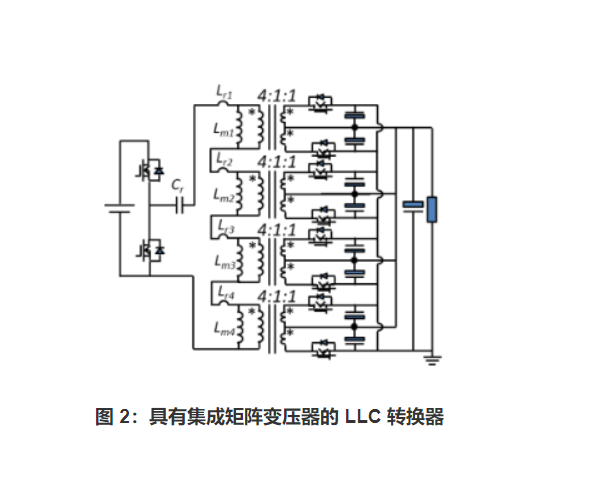

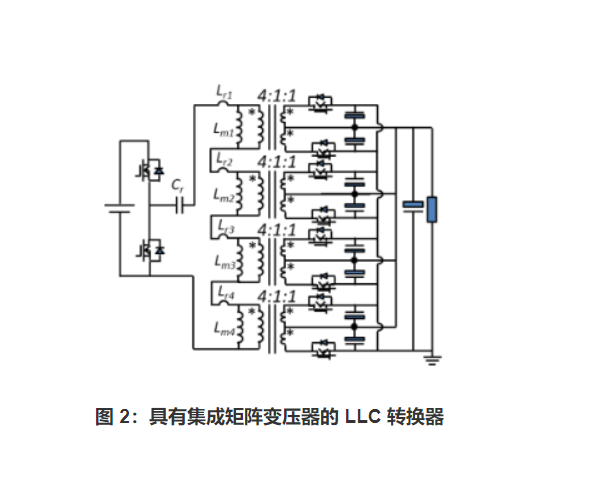

对于需要低电压、高电流输出的计算机服务器等应用,LLC 转换器设计面临电流共享方面的多个困难,以及集中在端接点处的高 di/dt 交流电流,导致显着的端接损耗。漏感、绕组损耗、重量和成本等问题仍然被证明是操作方面的一个负担。另一方面,平面PCB绕线变压器在自动化制造和高功率密度方面具有优势。它们使用矩阵变压器,确保次级电流均匀分布到 SR,以实用的方式解决设计挑战,特别是在集成到具有四核设计的结构化 LLC 转换器中时。下图 2 显示了常规 LLC 转换器如何与矩阵变压器集成。

具有集成矩阵变压器的 LLC 转换器

矩阵变压器采用四组 UI 磁芯,与单个 ER 磁芯设置相比,增加了磁芯损耗。为了缓解这一问题,对初级绕组进行修改可以消除磁通,从而减小磁芯尺寸和损耗。将 SR 和电容器集成到次级绕组中可最大限度地减少交流端接损耗,并使磁芯和 SR 的数量增加一倍。这不仅优化了设计,而且效率高达 97.1%,保持 700W/in 3的功率密度。然而,挑战依然存在,例如由于多核使用而导致制造复杂性,以及需要进一步提高效率以取代现有的较低频率运行的 DC/DC 转换器。

带 PCB 绕组的平面矩阵变压器的拟议架构

在设计DC/DC转换器时,主要目标是将380V降压至12V并输出67A,相当于800W。为了提高效率,采用了匝数比为 4:1:1 的四个元件变压器,并采用四层 PCB 绕组结构,初级绕组有两层,每层有两匝。选择 1MHz 的开关频率,并且圆形磁芯柱优于矩形磁芯柱,以减少绕组损耗。这一变化导致次级绕组的电流路径更短,从而进一步提高了效率。这种优化对于 LLC 转换器的高频矩阵变压器设计非常重要,因为它们平衡了功率密度和效率考虑因素。

人们提出了两种独特的矩阵变压器结构来解决多芯的挑战并提高效率。在结构1中,两个磁芯集成为一个,有效降低了与多个磁芯相关的复杂性。

结构 1 的通量分布

同时,结构2通过旋转一个磁芯并将其集成,进一步优化磁通分布,从而导致磁板内的磁通密度显着降低。磁通密度的降低意味着磁芯损耗的降低,这对于高频铁氧体材料尤其有利,因为磁芯损耗是影响整体效率的关键因素。仿真结果表明,与结构 1 相比,结构 2 减少了约 40% 的磁芯损耗,使其成为效率和鲁棒性方面的最佳选择,因为它对基本变压器之间的容差变化不太敏感。

结构 2 中的绕组布置也有助于其优越性,更均匀分布的磁通模式可降低磁芯损耗,结构 2 中四个基本变压器的耦合增强了稳健性和可靠性。所提出的设计将次级绕组与肖特基整流器 (SR) 和输出电容器等组件集成,以有效减轻交流端接损耗。通过利用四层 PCB 绕组实现,该设计简化了结构,同时降低了绕组间电容和总体 PCB 成本。建议对结构 2 进行进一步增强,以在不牺牲功率密度的情况下最大限度地减少磁芯损耗,从而确保 LLC 转换器应用中的最佳性能。

结论

进行了一项实验来研究高输出电流 LLC 转换器的矩阵变压器。提出了一种设计,将四个基本变压器集成到一个磁芯中,并在简单的四层 PCB 上进行绕组。由于磁通抵消和磁通密度降低,与最先进的技术相比,该设计将磁芯损耗减少了一半以上。此外,它将输出电容器和SR集成到次级绕组中,最大限度地减少泄漏和端接损耗。

借助 GaN 器件,所提出的设计可实现更高的开关频率,从而提高效率、功率密度和可制造性。使用所提出的结构的1MHz 380V/12V 800W LLC转换器原型实现了97.6%的峰值效率和900W/inch 3的功率密度。

10万+粉丝交流 了解更多物联网技术知识请

关注微信公众号:计算机程序吧